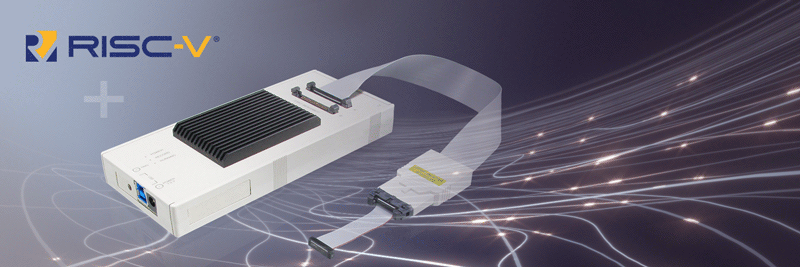

Lauterbach extends its range of RISC-V debuggers by the release of an additional µTrace.

All Lauterbach RISC-V debug tools are designed to work with the latest ratified RISC-V debug specification. The low-cost µTrace is aimed at small, very low cost, low power 32-bit RISC-V designs; the kind of devices that would typically be used for IoT, AI, or microcontrollers. It is designed to provide full debug access to 32-bit RISC-V processors, either in a single-core or multi-core design. The TRACE32 PowerView software includes a well-documented API, allowing users to extend the disassembler to support custom instructions. The µTrace will interface to a 20-pin debug header or the RISC-V defined MIPI10 and MIPI20T headers.

RISC-V is an open Instruction Set Architecture that allows designers to create chips with a well-defined instruction set, custom peripherals, yet remain royalty free. Originally developed at UC Berkely in 2010, today it is maintained by the non-profit RISC-V International Consortium. The RISC-V specification allows for 32-bit (RV32), 64-bit (RV64) and 128-bit (RV128) instruction sets with a number of ratified extensions to add functionality such as: floating point, atomic operations, multiplication, compressed instructions, and standard debug, etc.

µTrace will be available from 1st January 2021.